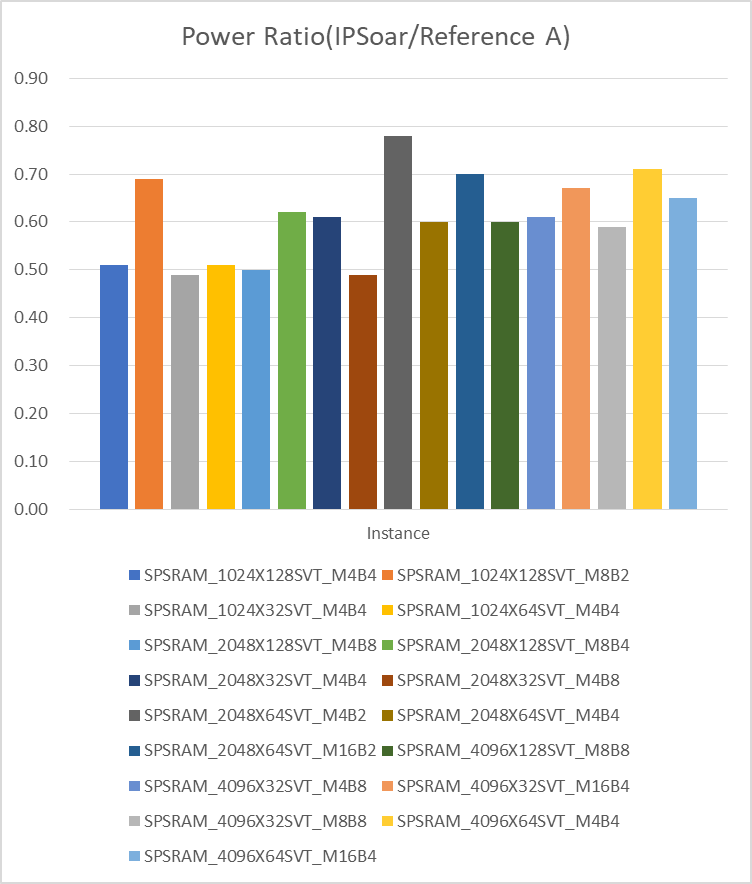

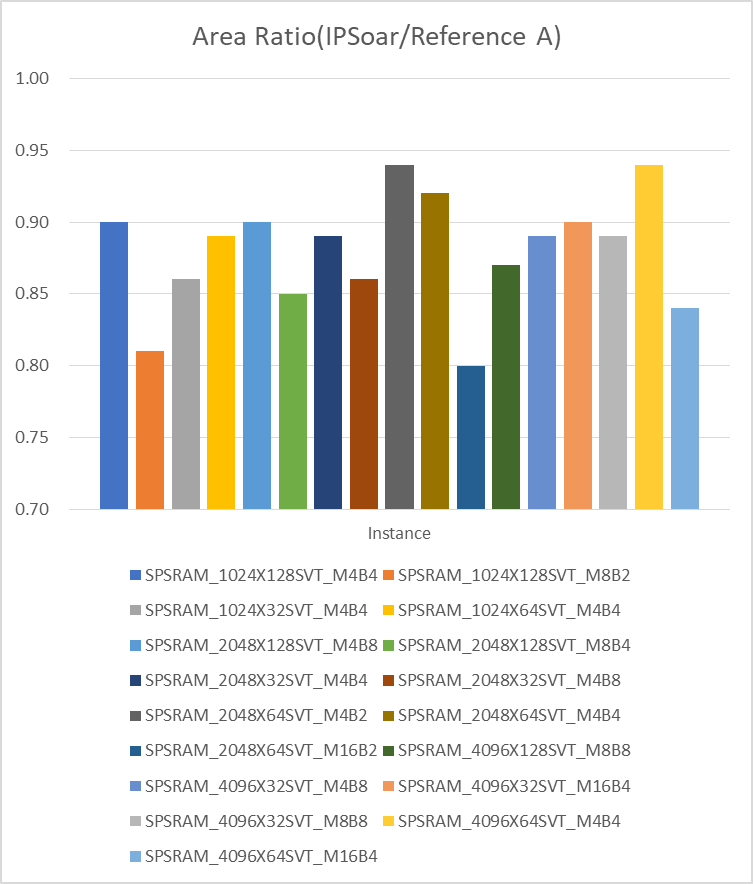

IPSOAR 提供了业界极具竞争力的memory compiler产品,通过全手工定制打造Memory compiler产品,满足客户在面积、速度、功耗上的极致需求,帮助客户提高产品竞争力。

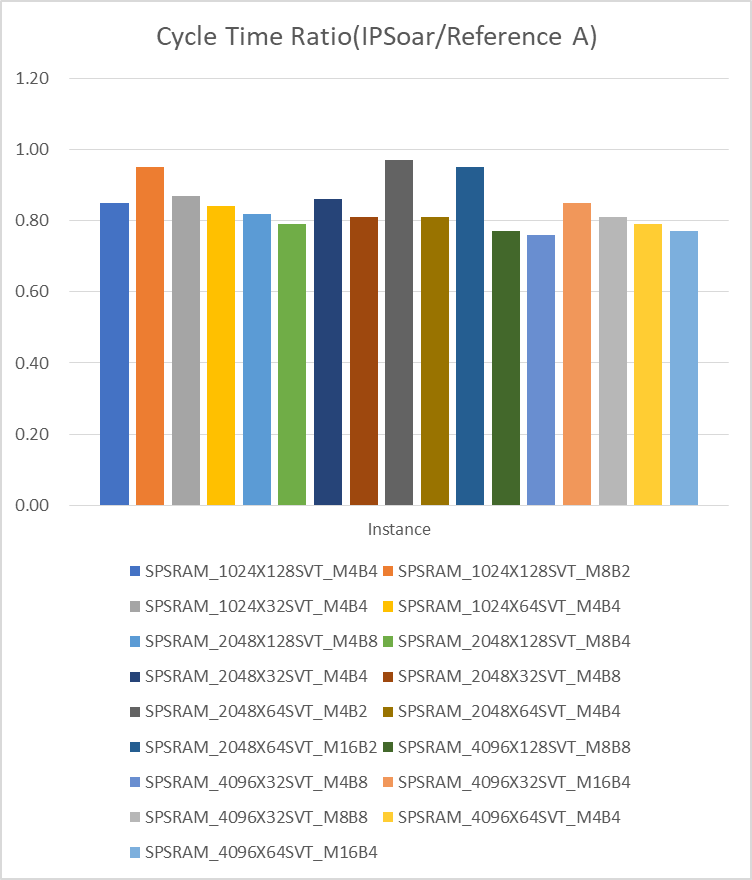

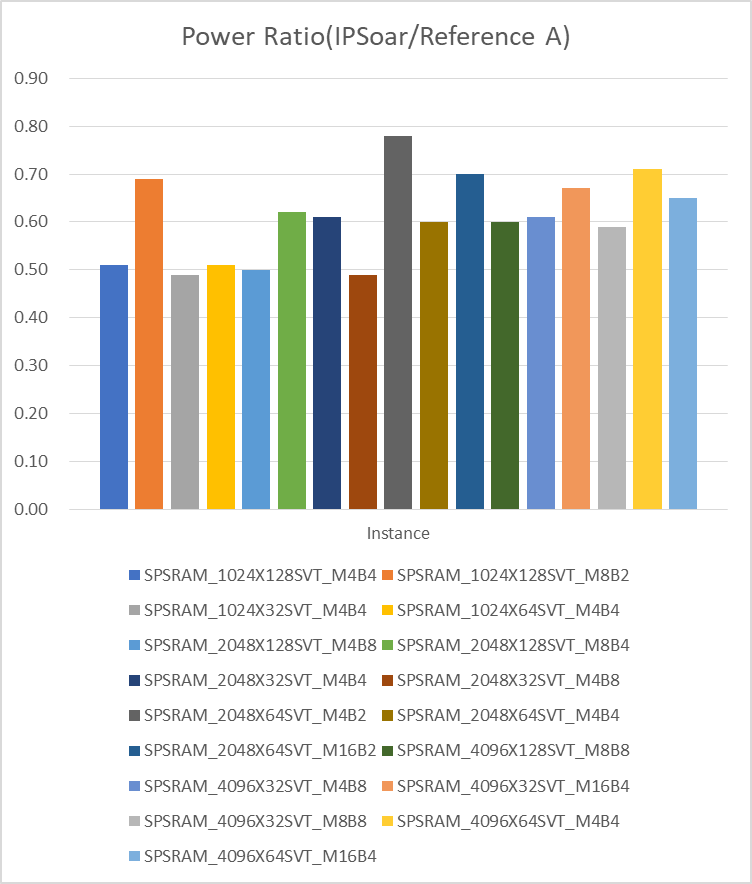

IPSOAR memory compiler通过独有的低功耗设计方案,静态漏电流同比业界降低30~50%;同时支持三种低功耗模式(Nap,Retention,Power down),满足客户对不同低功耗模式下的需求。

IPSOAR memory compilers 提供了业界领先的EDA 模型,包括datasheet, verilog behavior mode, liberty model, P&R model, DFT model等。

能够提供工艺节点从0.18um 到 7nm 先进工艺平台的产品。

Highlights:

IPSOAR memory compiler通过独有的低功耗设计方案,静态漏电流同比业界降低30~50%;同时支持三种低功耗模式(Nap,Retention,Power down),满足客户对不同低功耗模式下的需求。

IPSOAR memory compilers 提供了业界领先的EDA 模型,包括datasheet, verilog behavior mode, liberty model, P&R model, DFT model等。

能够提供工艺节点从0.18um 到 7nm 先进工艺平台的产品。

Highlights:

● Process variation tolerance design technique to improve yield

● Reduce memory hard failure to improve yield by considering critical DFM rule

● Auto leakage control technique to reduce standby current

● Fully customized and optimized layout to get minimum area

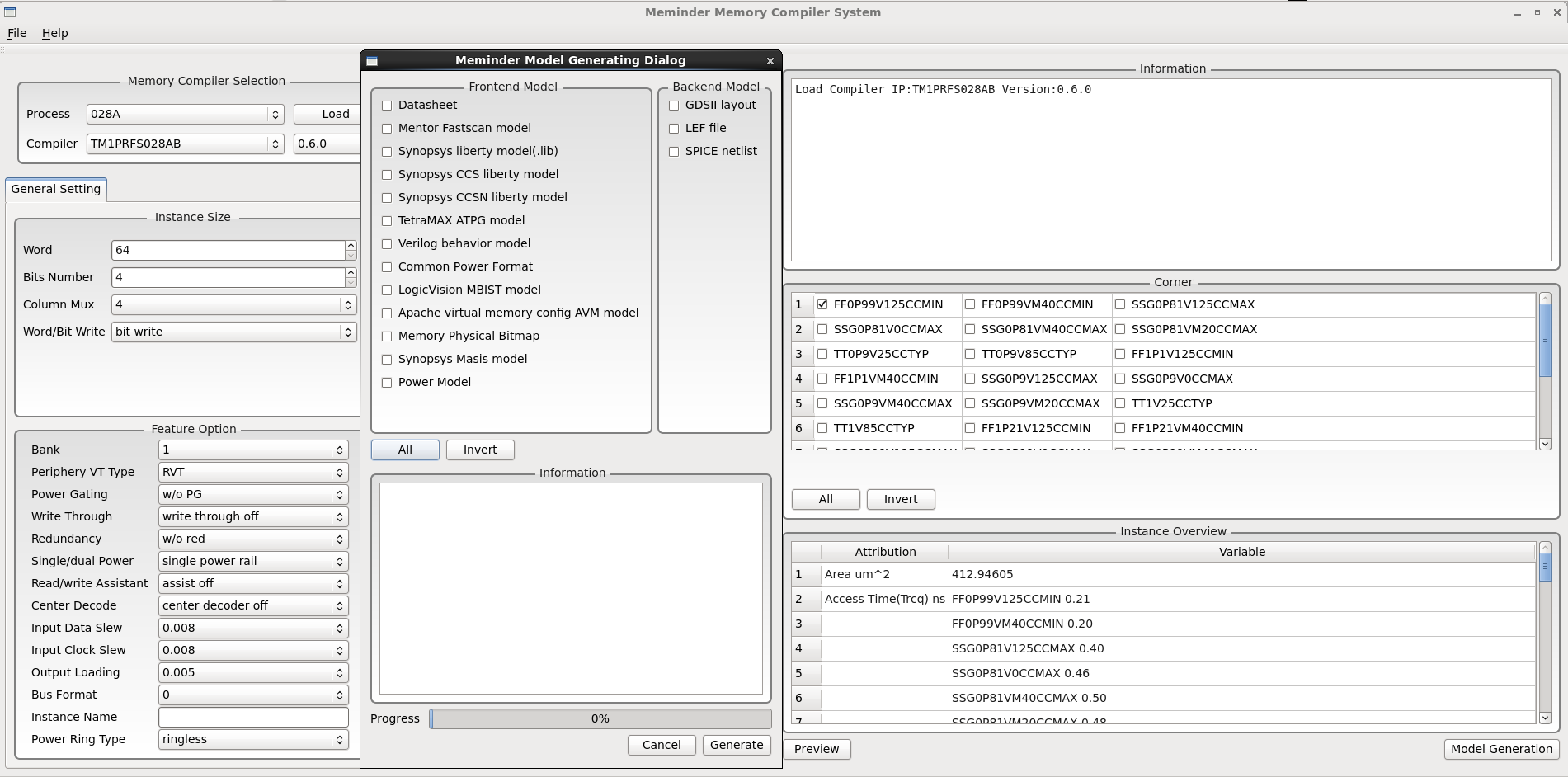

● Ultra faster memory compiler engine “Meminder” to generate memory instance rapidly

Deliverables:

可视化图形界面:

Deliverables:

● Verilog timing/simulation model

● VHDL timing/simulation model

● Spice-level netlist for LVS

● GDSII layout database

● Physical bitmap support

● Timing/Power/Noise liberty model

● P&R model

● Memory BIST model

可视化图形界面:

| Products | Memory Type |

|---|---|

| Memory Compiler | High Density Single Port SRAM |

| High Density One Port Register File | |

| High Speed Single Port SRAM | |

| High Speed One Port Register File | |

| Two Port Register File | |

| Two Port SRAM | |

| Dual Port SRAM | |

| Ultra high density two port register file (one clock) | |

| Ultra high density two port SRAM (one clock) | |

| Via ROM | |

| TCAM | |

| Special Multi-Port SRAM |